ISSN(O): 2319-8753

ISSN(P): 2347-6710

# International Journal of Innovative Research in Science Engineering and Technology (IJIRSET)

(A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

**Impact Factor: 8.699**

Volume 14, Issue 7, July 2025

www.ijirset.com | A Monthly, Peer Reviewed & Refereed Journal | e-ISSN: 2319-8753 | p-ISSN: 2347-6710

Volume 14, Issue 7, July 2025

|DOI: 10.15680/IJIRSET.2025.1407098|

## Design and Performance of Different Low Power Full Adder Topologies using CMOS Technology

A. Jeba Ofila, S. I. Padma, Dr. K. Madhan Kumar, K. Rahmath Nisha

PG Student, Dept. of ECE, PET Engineering College, Vallioor, Tamil Nadu, India Associate Professor, Dept. of ECE, PET Engineering College, Vallioor, Tamil Nadu, India Professor, Dept. of ECE, PET Engineering College, Vallioor, Tamil Nadu, India Assistant Professor, Dept. of ECE, PET Engineering College, Vallioor, Tamil Nadu, India

ABSTRACT: In this project different types of Full Adder are designed using CMOS Technology. To implement Complementary Metal Oxide Semiconductor (CMOS)Logic technology many logic styles are employed, one example is full adder which is the circuit one of the most important digital functional blocks used in arithmetic and logic unit. The proposed full adder topologies present different low power and high-speed full adder designs for digital arithmetic circuits: 6T,8T and 10T. Each design uses a different number of transistors to implement the full adder, achieving varying level of power consumption and speed. The aim of this project is to design a different full adder design using CMOS with low consumption of power and high performance. The proposed full adders circuits are designed using 0.12µm CMOS technology at 1.2V supply voltage. DSCH is used to validate the architecture of the logic circuit and Microwind tool is used for designing and simulating circuits at layout level.

KEYWORDS: CMOS; Full adder; Power consumption; Layout.

#### I. INTRODUCTION

Binary addition is facilitated by a fundamental digital component known as a full adder. This circuit combines three input bits, producing a sum and a carry-out signal. The full adder plays a critical role in digital arithmetic, enabling computers and other electronic devices to perform calculations. By processing three inputs and generating two outputs, the full adder ensures accurate binary addition, including the transfer of values to subsequent bit positions. This essential function makes the full adder a cornerstone of digital electronics and computing systems.

#### II. FULL ADDER

In digital electronics, full adders serve as essential building blocks for arithmetic operations. By integrating three binary inputs, these circuits produce a sum and carry-out signal, facilitating precise calculations. The full adder's ability to handle binary addition with carry-over values makes it a crucial component in various digital systems, from simple calculators to complex computing architectures. Its functionality enables efficient and accurate processing of binary data, underpinning many modern technological advancements.

#### III. PROPOSED FULL ADDER DESIGN

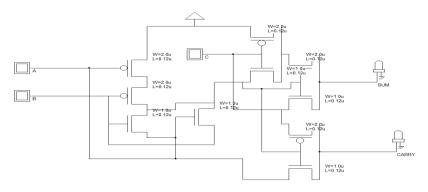

A 10-transistor full adder is a highly optimized design used in low power, high speed digital circuit. The proposed 10T full adder is achieve low power consumption, high speed and reduced transistor count compared to conventional full adders. The proposed circuit is built using 5 NMOS and 5 PMOS transistors. Four transistors for XOR logic and Six transistors for MUX based approach.

www.ijirset.com | A Monthly, Peer Reviewed & Refereed Journal | e-ISSN: 2319-8753 | p-ISSN: 2347-6710 |

### Volume 14, Issue 7, July 2025

### |DOI: 10.15680/IJIRSET.2025.1407098|

Fig 1 Proposed 10T full adder design

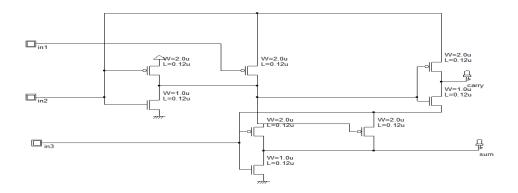

A novel design of 8T full adder designed on the logic of two 3T XOR and one 2T MUX.So in total 8 transistor.

Fig 2 Proposed 8T full adder design

The 6-transistor full adder is an ultra-compact and efficient arithmetic circuit design using PTL. The proposed 6T FA designed using two 2T XOR and one MUX. The proposed full adders achieve better result than 8T,10T in terms of power, delay and power delay product. The 6T full adder circuit is designed using  $0.12\mu m$  CMOS technology at 1.2V supply voltage.

Fig 3 Proposed 6T full adder design

www.ijirset.com | A Monthly, Peer Reviewed & Refereed Journal | e-ISSN: 2319-8753 | p-ISSN: 2347-6710 |

### Volume 14, Issue 7, July 2025

### |DOI: 10.15680/IJIRSET.2025.1407098|

Table 1 Comparison between Full Adder and Proposed Full Adder design

| Design         | Number<br>Of<br>Transistor | Power<br>(mW) | Delay<br>(ns) | PDP   |

|----------------|----------------------------|---------------|---------------|-------|

| Full Adder     | 28                         | 5.55          | 19.67         | 109   |

| 10T Full Adder | 10                         | 0.439         | 8             | 3.312 |

| 8T Full Adder  | 8                          | 0.368         | 3.018         | 1.11  |

| 6T Full Adder  | 6                          | 0.25          | 1.95          | 0.492 |

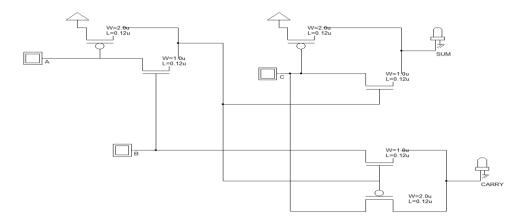

#### IV. SIMULATION RESULTS

The proposed full adder with minimum of 8 transistor with high speed and low power consumption, which employs a two 3T XOR and 2T MUX. The proposed 10T circuit is built using 5 NMOS and 5 PMOS transistors. Four transistors for XOR logic and Six transistors for MUX based approach. The proposed full adder schematics are drawn using  $0.12\mu m$  CMOS technology with 1.2~V supply voltage. Simulation results shows the great improvement in terms of power delay product. The 6T full adder consumes an average power of 0.252mW. The power consumption increases with the number of transistors. The critical path delay of the 6T FA measured at 0.492~ps.

Fig 4 shows Microwind layout of 8T full adder using 0.12μm CMOS technology with 3 input and 2 output.

Fig 4 Layout Design of the Proposed Full Adder

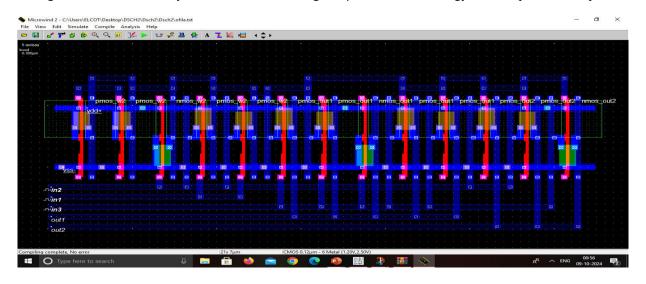

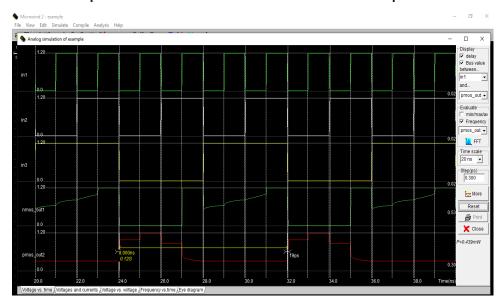

The power consumption of a proposed 10T full adder is 0.439 mW. Fig 5 shows simulated output waveform of voltage vs time with 0.439 mW. Delay of the 10T full adder is 8 ns. The power delay product(PDP) of 10T full adder is 3.512 aJ.

|www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

### Volume 14, Issue 7, July 2025

### |DOI: 10.15680/IJIRSET.2025.1407098|

Fig 5 Simulated Output Waveform of 10T Full Adder Design

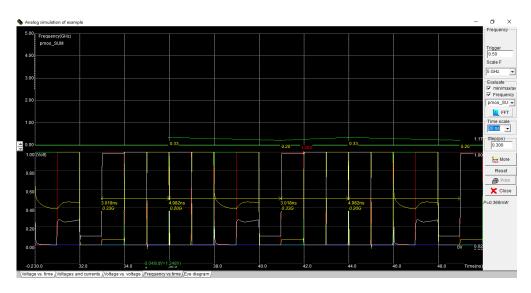

The power consumption of a proposed 8T full adder is 0.368mW. Fig 6 shows simulated output waveform of voltage vs time with 0.368 mW power.delay of the 8T full adder is 3.018 ns. The power delay product(PDP) of 8T full adder is 1.11aJ.

Fig 6 Simulated Output Waveform of 8T

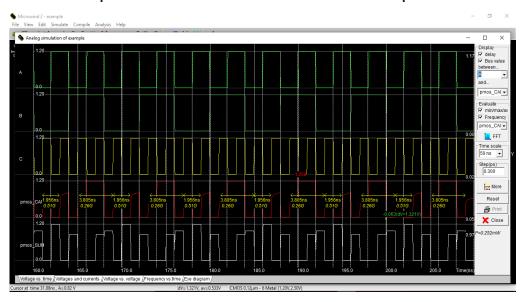

The power consumption of a proposed 6T full adder is 0.252 mW. Delay of the 8T full adder is 1.956ns. The power delay product (PDP) of 6T full adder is 0.492 aJ.

www.ijirset.com | A Monthly, Peer Reviewed & Refereed Journal | e-ISSN: 2319-8753 | p-ISSN: 2347-6710 |

### Volume 14, Issue 7, July 2025

### |DOI: 10.15680/IJIRSET.2025.1407098|

Fig 7 Simulated Output Waveform of 6T

#### V. CONCLUSION

In this paper different types of Full Adder are designed using CMOS Technology. A novel design of 8T full adder, which is designed on the logic of two 3T XOR and one 2T MUX. The proposed 10 transistor full adder is designed using 5 PMOS and 5 NMOS CMOS logic style. The 6T FA designed using two 2T XOR and 2T MUX. The Proposed Full Adder is simulated using the DSCH tool and 3D layout of Proposed Full Adder is designed using Microwind tool. The Power supply of the Proposed full adder is 1.2 voltage. The Small number of transistors has higher performance. The power consumption and of the proposed 10T full adder is 0.439mW. The delay of the eight transistor full adder is 8 ns. The power consumption and of the proposed 8T full adder is 0.368 mW. The delay of the eight transistor full adder is 3.018 ns. The 6T Full adders has an improvement for various parameters like power consumption, speed performance and structure size. The power consumption and of the proposed 6T full adder is 0.252 mW. The delay of the six transistor full adder is 1.956 ns. which is lower than the conventional full adder. The proposed 6T full adder gives better calculation of PSD by using 0.12µm CMOS technology. The Power Delay Product of 6 transistor full adder is 0.492. The proposed full adders achieve better result than 8T,10T in terms of power, delay and power delay product. It is suitable for low energy application and portable devices.

#### REFERENCES

- 1. Veena M.B, Suhana Khanum N, Soundaryya D.H,"XNOR-XOR based Full Adder Using Double Pass Transistor Logic", International Journal on Advances in Electronics, Communication, Computing and Intelligent Information Systems (ICAECIS) | IEEE | DOI:10.1109/ICAECIS58353.2023.10169925,2023.

- 2. S.Kifayat Kabir, Chamak Ganguly, Khandaker Arefin," Analysis of a 10T Full Adder with a new 4T X-NOR using FD-SOI 22nm Mix-VT Technology, International Journal of Electrical and Computer Engineering, 2023.

- 3. Sehan Amandu Gamage, Krishnan Subramaniam, Ahmad Anwar Zainuddin "Comparative Analysis of CMOS based Full Adders by Simulation in DSCH and Microwind", Malaysian Journal of Science and Advanced Technology, MJSAT, 2022.

- 4. Aibin Yan, Han Bao, Wangjin Jiang,"Efficient Design Approaches to CMOS Full Adder", International Journal of Recent Technology and Engineering (IJRTE),2022.

- 5. Sparsha A.C, Sree Rekha K.P, Akshara S, B.P Harish,"Design Space Exploration Of Low Power Full Adder Across Multiple Logic Styles And Process", International Journal of Engineering Applied Sciences and Technology, Vol. 7, Issue 9, ISSN No. 2455-2143, Published Online January 2023 in IJEAST (http://www.ijeast.com), 2022

- 6. Mehedi Hasan, Abdul Hasib Siddique, Abdal Hoque Mondol," Comprehensive study of 1-Bit full adder cells", SN Applied Sciences a sparing natural journl,2021.

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

### **Volume 14, Issue 7, July 2025**

### |DOI: 10.15680/IJIRSET.2025.1407098|

- 7. Ashish Bagwari, Isha Katna,"Low Power Ripple Carry Adder Using Hybrid 1-Bit Full Adder Circuit",978-1-5386-8439IEEE,DOI:10.1109/CICN.2019.22 ,2019.

- 8. Benjamin Franklin A, Sasilatha T, "Design and Analysis of Low Power Full Adder for Portable and Wearable Applications", International Journal of Recent Technology and Engineering, 2019.

- 9. Majid Amini-Valashani, Mehdi Ayat, Sattar Mirzakuchaki," Design and analysis of a novel low-power and energy-efficient 18T hybrid full adder", IOSR Journal of VLSI and Signal Processing (IOSR-JVSP)Volume 5, Issue 1, p-ISSN No.: 2319 4197, DOI: 10.9790/4200-05116065 www.iosrjournals.org, 2018.

- 10. Nagaraju N, Ramesh S.M, Soundharya V, Sowmiya K," Design and Implementation of Efficient Adder Using Various Logic Styles", International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056 Volume: 05 Issue: 02 | Feb-2018 www.irjet.net p-ISSN: 2395-0072,2018.

- 11. Khoirom Johnson Singh, Tripurari Sharan, Huirem Tarunkumar," High Speed and Low Power Basic Digital Logic Gates", Journal of VLSI Design Tools & Technology Journal of VLSI Design Tools & Technology ISSN: 2249-474X (Online), ISSN:23216492,www.stmjournals.com,2018.

- 12. Arvind Nigam, Raghvendra Singh," High Speed and Low Power Basic Digital Logic Gates Half Adder and Full Adder using Modified Gate Diffusion Input Technology", Journal of VLSI Design Tools & Technology, 2018.

- 13. Manjunath ,Amarappa Pagi,Ulaganathan ,"Analysis of Various Full-Adder Circuits in Cadence",International Journal of Computer Applications ,2015.

- 14. Partha Bhattacharyya, Bijoy Kundu, Sovan, Vinay Kumar," Performance Analysis of a Low-Power High-Speed Hybrid 1-bit Full Adder Circuit", IEEE ,2014.

- 15. Raj Johri,Raghvendra Singh,Shyam Akashe,"Comparative Analysis of 10T and 14T Full Adder at 45nm Technology", IEEE,2012.

## INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

9940 572 462 🔯 6381 907 438 🔀 ijirset@gmail.com